Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 1

# ONFI 3.2 and Flash Control Basics

## High-Speed Memory Systems: **Architecture and Performance Analysis**

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 2

# **Open NAND Flash Interface—Basics**

- The command set

- Addressing and activation

- Figuring out what you're attached to

- Command overview, including concurrent accesses

- **NV-DDR and NV-DDR2 interfaces**

$\nabla$

Memory Systems

University of Crete

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 4

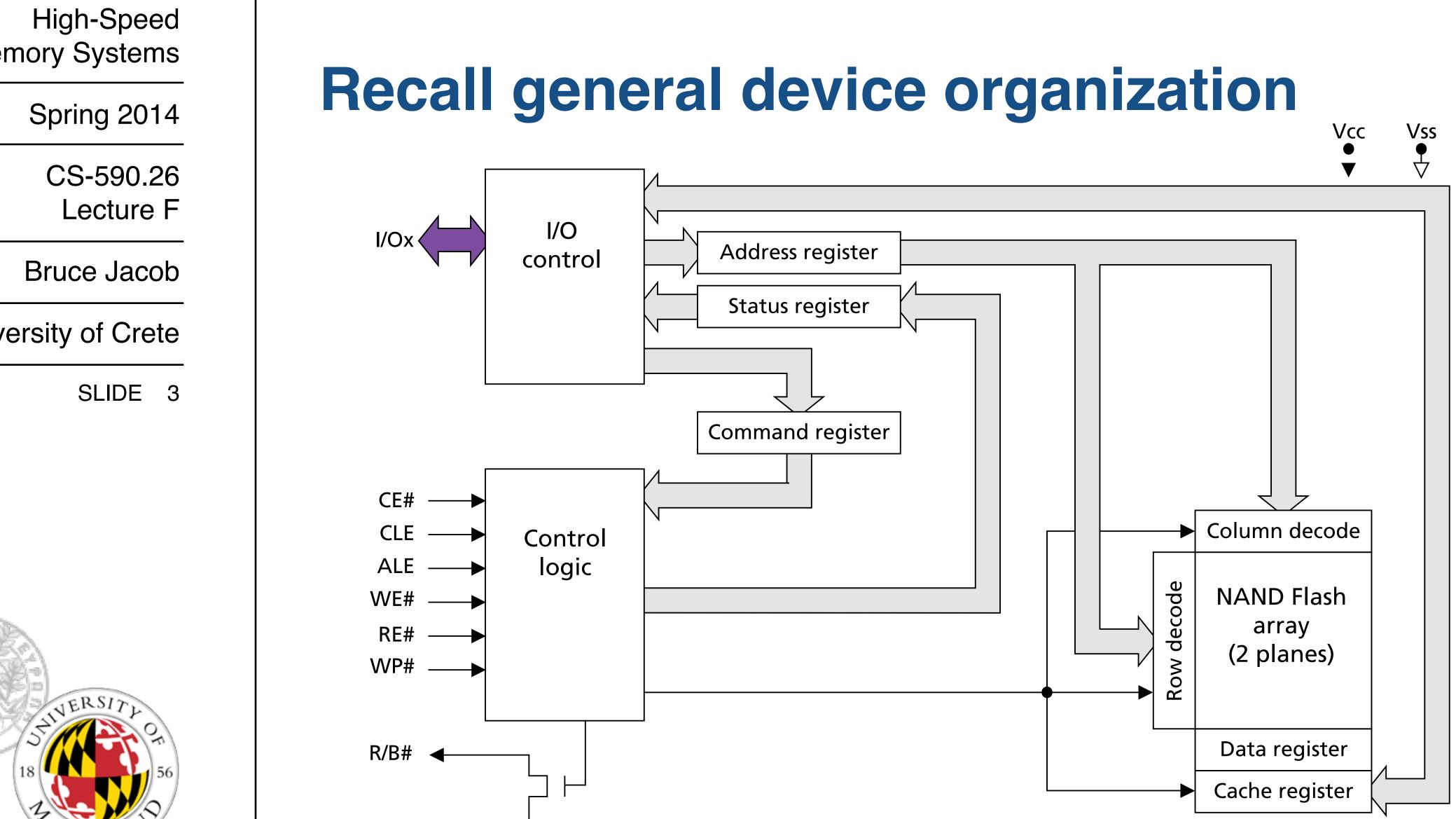

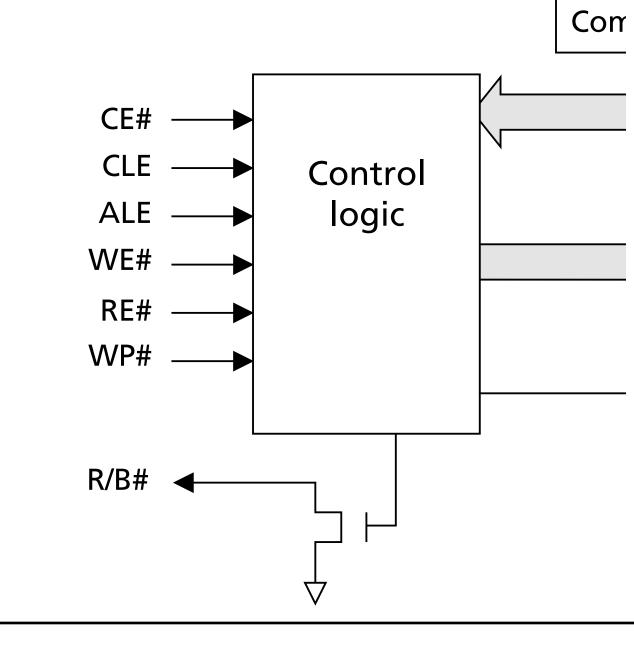

# **Recall general device organization**

- Control signals ('#' = active low)

- **CE# Chip Enable**

- **CLE Command Latch Enable**

- ALE Address Latch Enable

- WE# Write Enable

- **RE# Read Enable**

- WP# Write Protect

- R/B# Read/Busy (from SR[6])

There is also a CLK ...

## **Three Interfaces:**

- SDR what used to be called "asynchronous" — can be 8-bit or 16-bit relatively slow

- **NV-DDR**  used to be called "source-synchronous" — must be 8-bit

- NV-DDR2 — must be 8-bit - up to 267MHz, 533MT/s = 533MB/s

High-Speed Memory Systems

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 5

- up to 100MHz, 200MT/s = 200MB/s

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 7

# VERSI 18

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 9

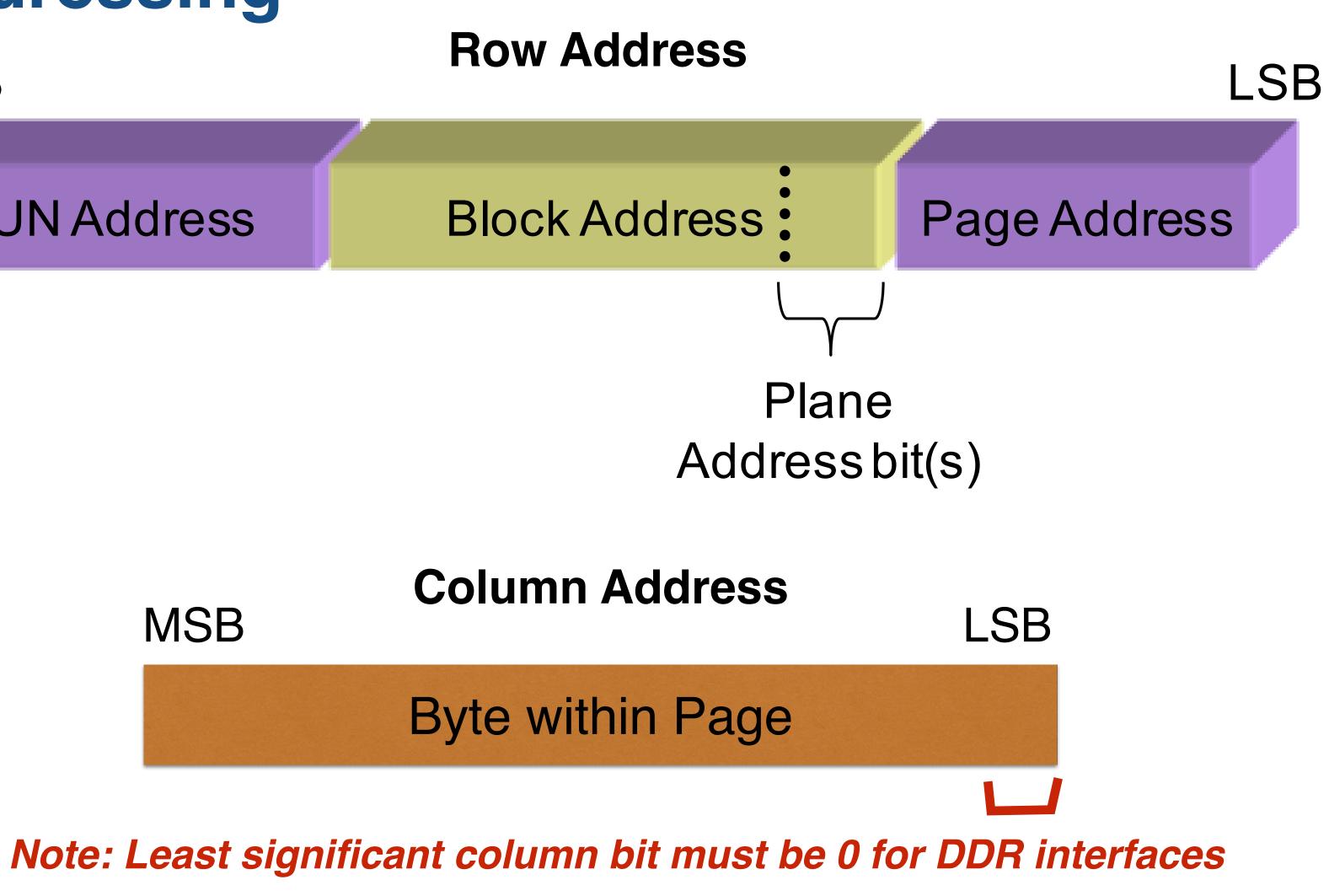

### Addressing MSB

### **LUN Address**

### This is easy

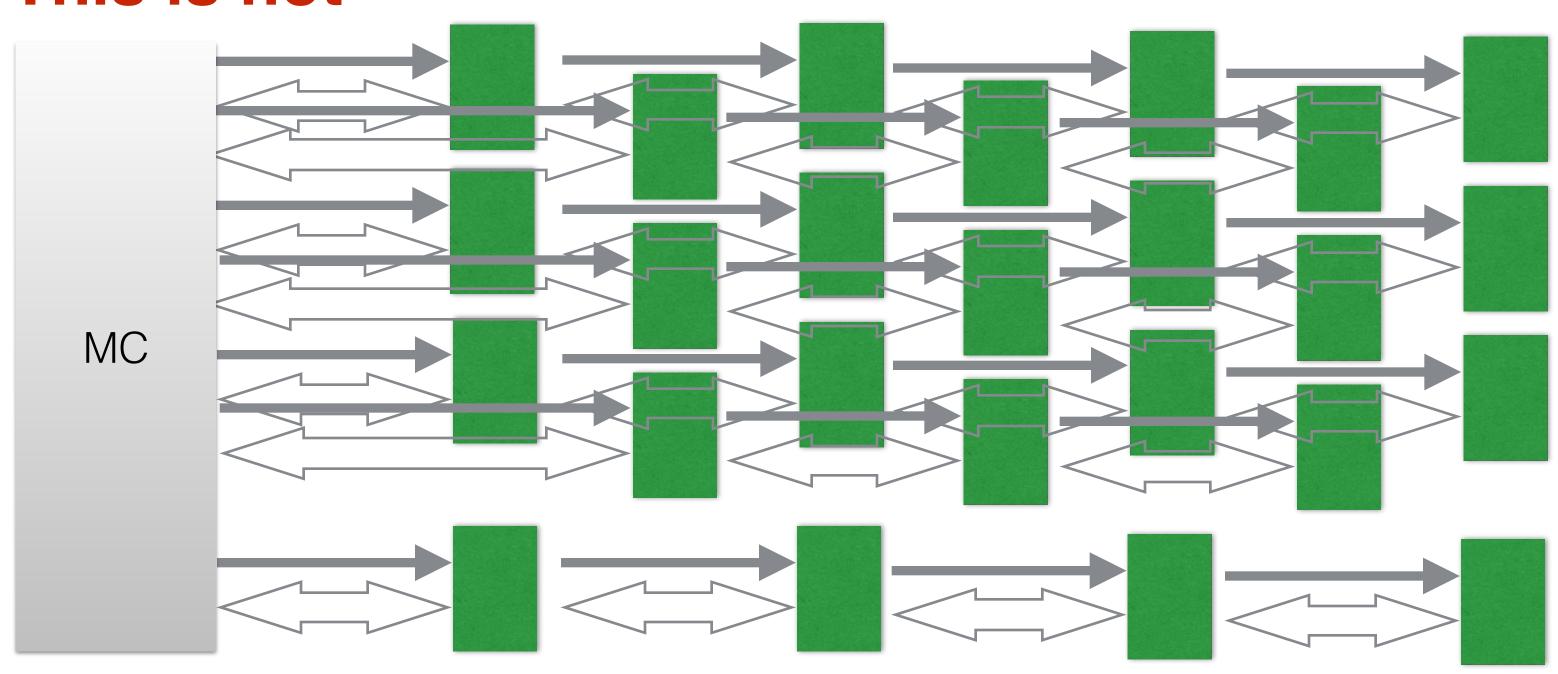

### This is not

High-Speed Memory Systems

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 11

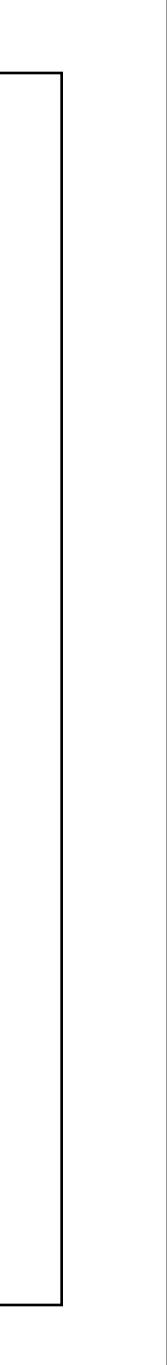

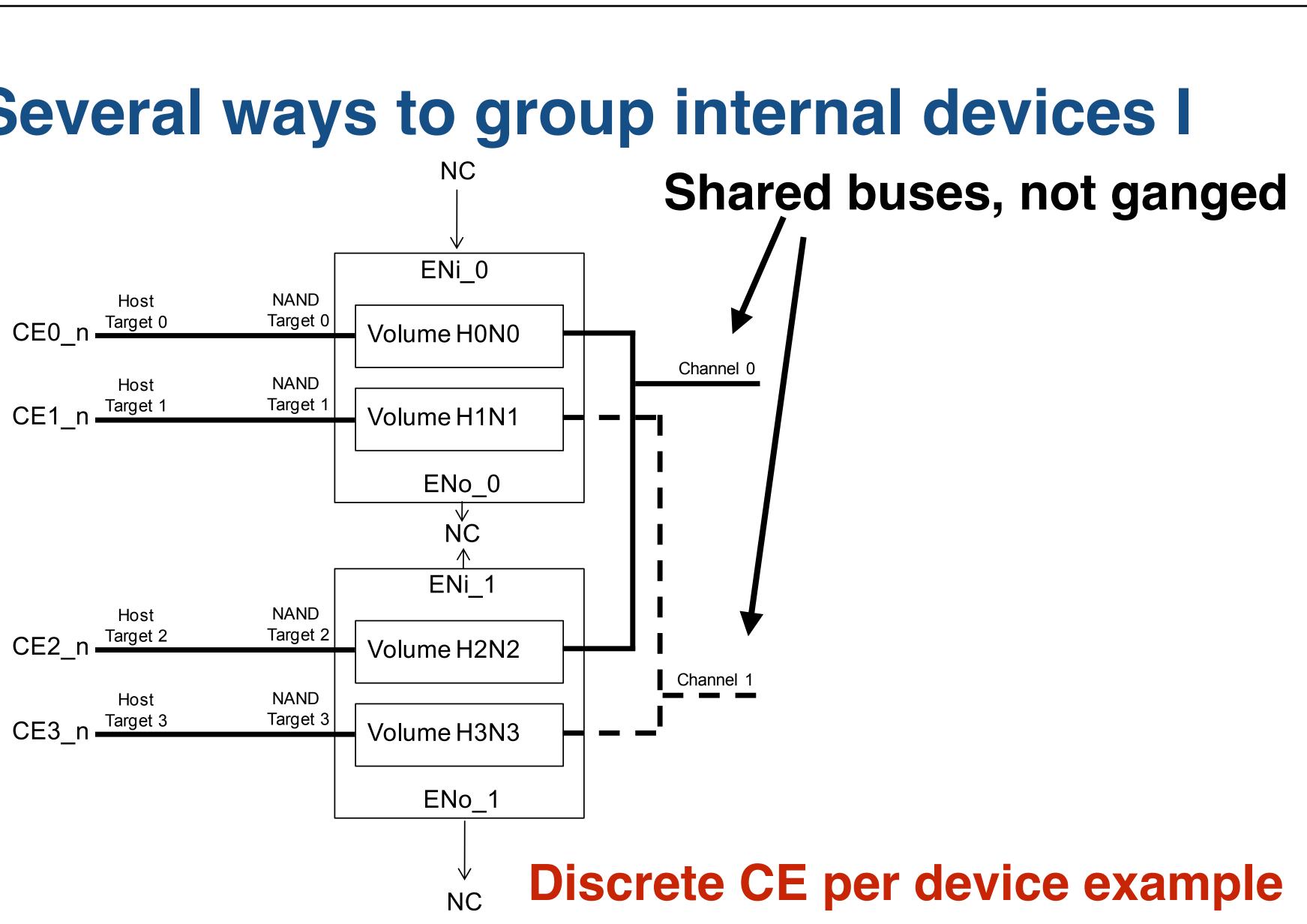

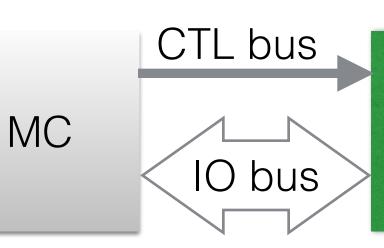

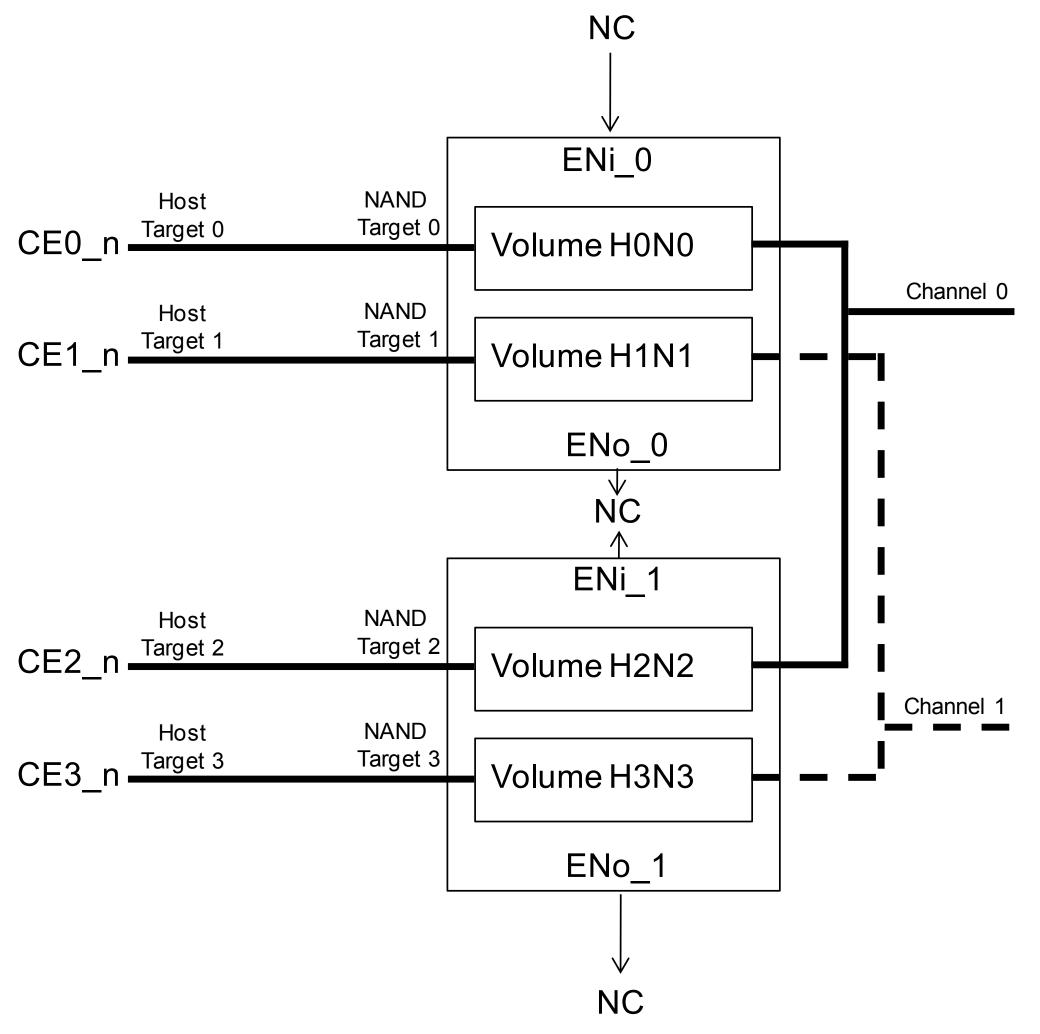

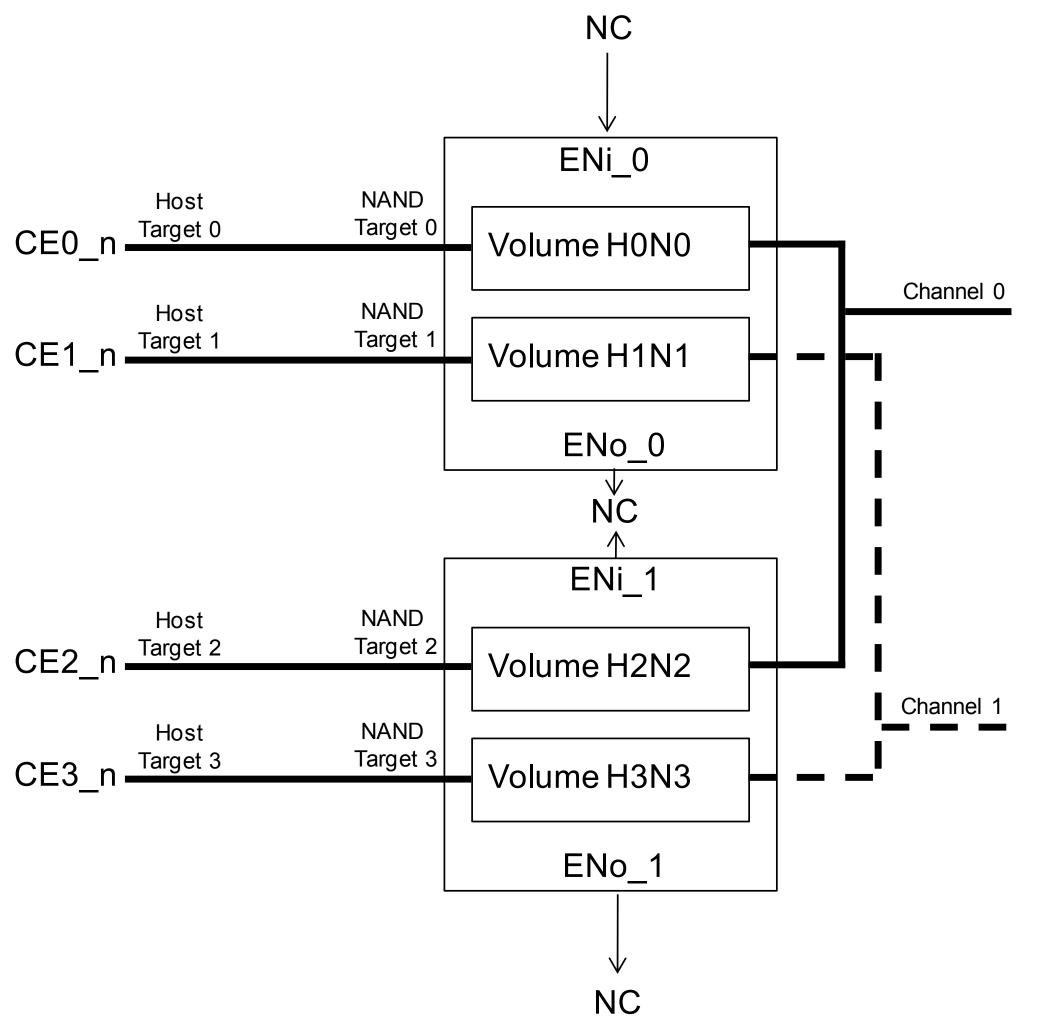

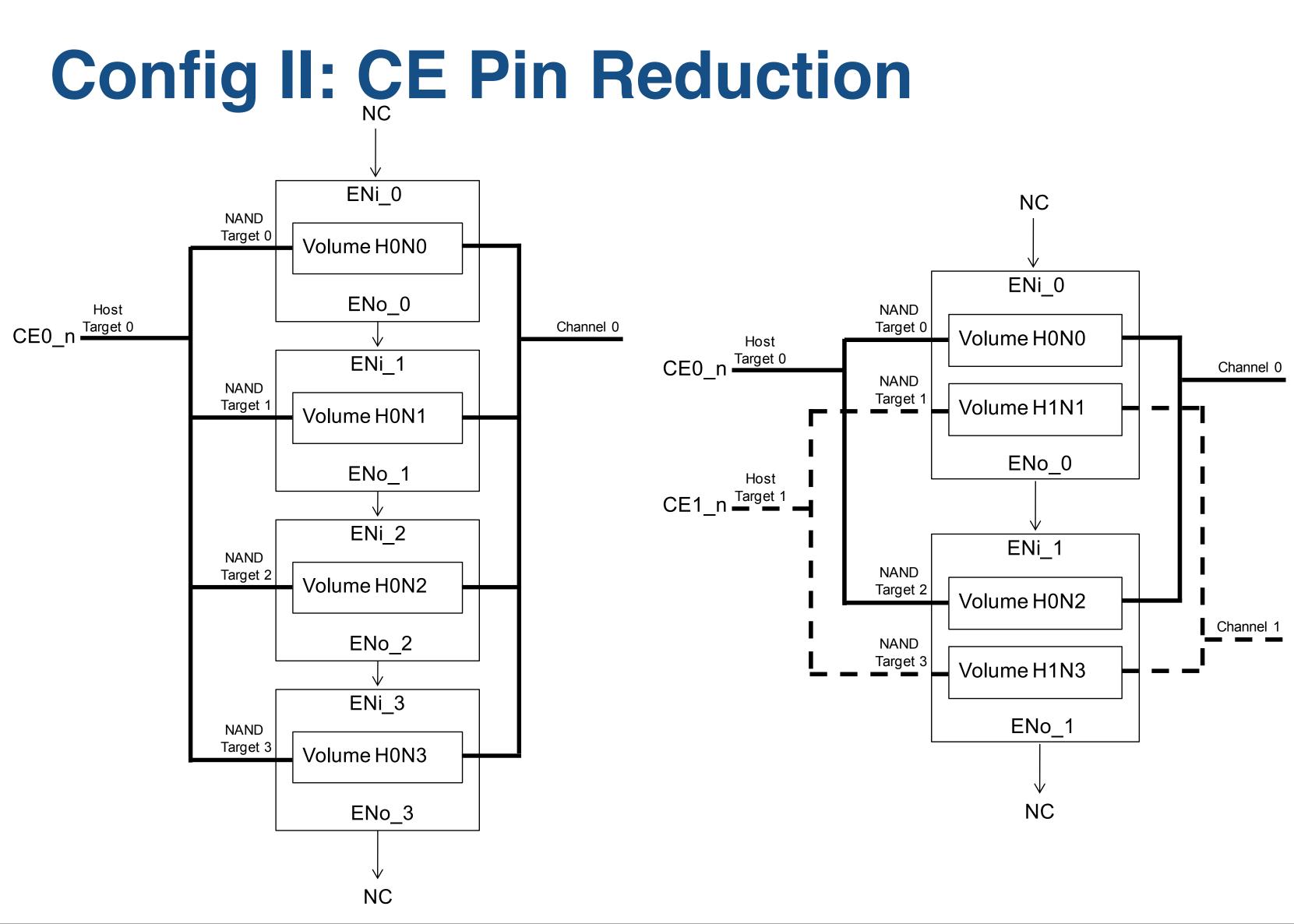

### **Config I: Discrete CE per Device**

**Config I: Discovery**

Pull CE\_i low

Using I/O Bus j:

Next CE pin else ....

High-Speed Memory Systems

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

- Foreach distinct CE pin i, in order from CE\_0 to CE\_7:

- Foreach distinct 8-bit bus j (could be up to 4):

- **Issue Reset (FFh) command**

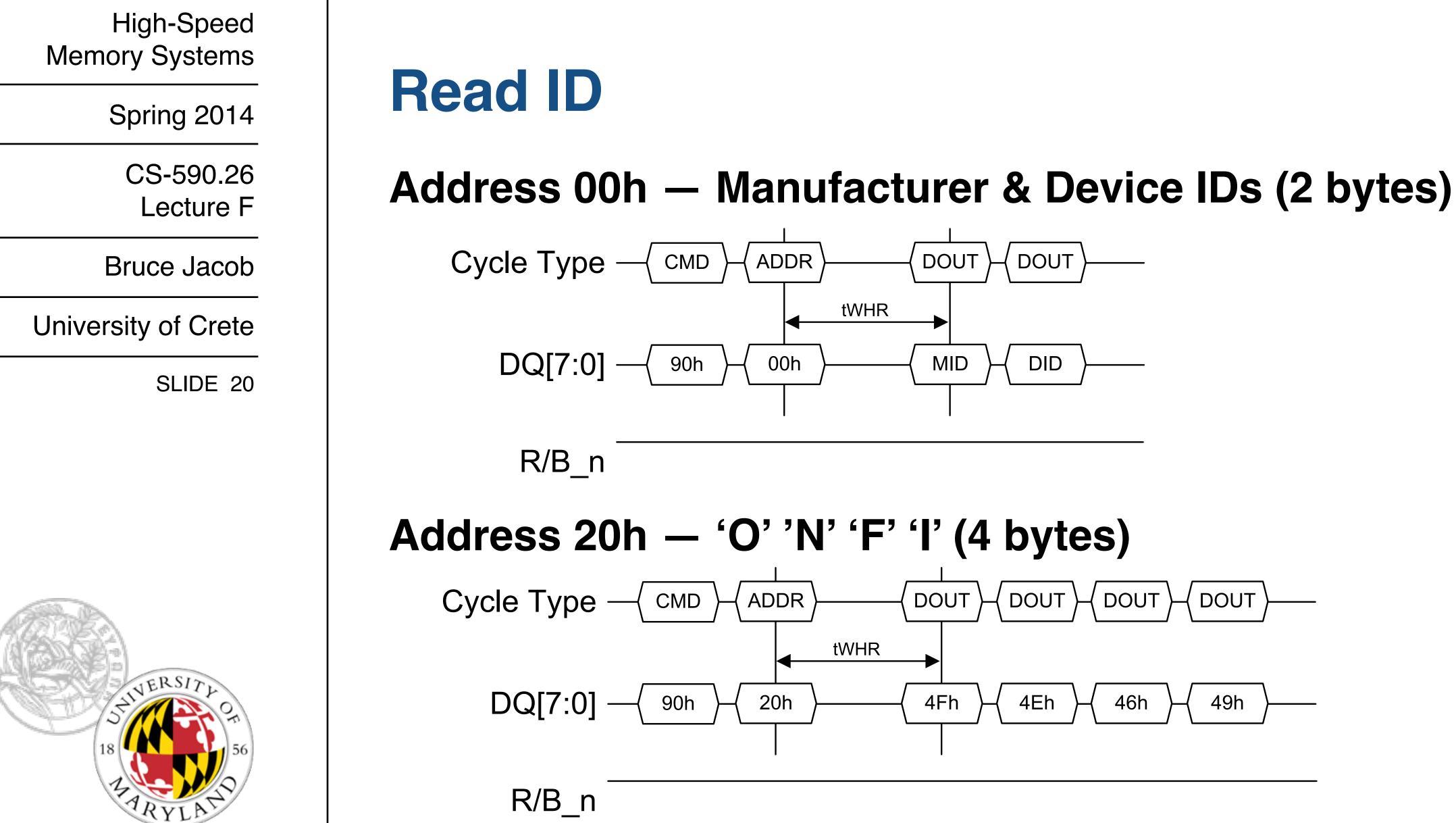

- Issue Read ID (90h) command with address 20h

- If ONFI signature is returned Make a note that CE\_i + Bus j is valid combo

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 14

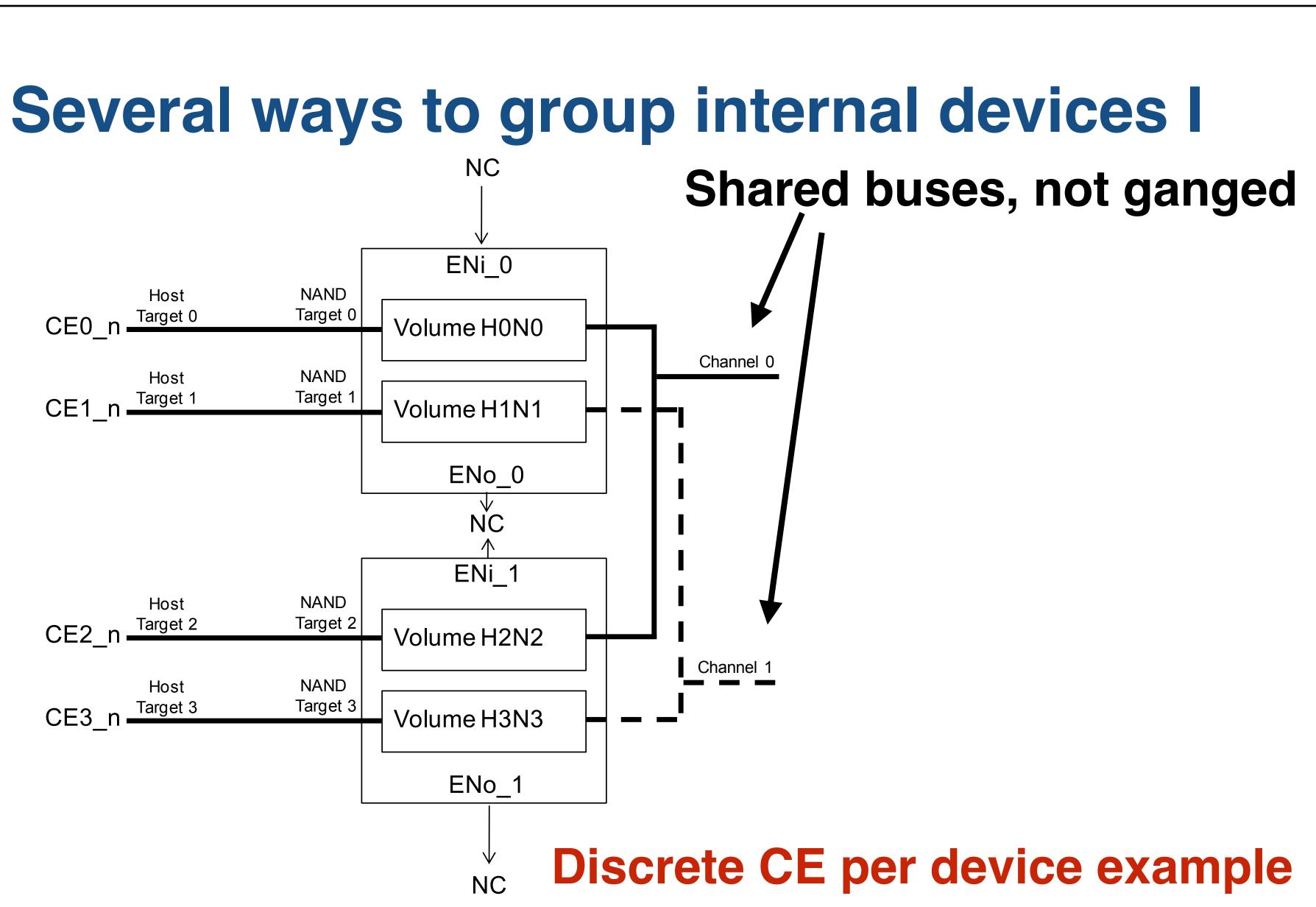

### **Config II: Discovery**

1. Power is applied to the NAND device(s).

2. CE\_n (Host Target) is pulled low.

3. If resetting all NAND Targets in parallel, then the host issues the Reset (FFh) command. This command is accepted by all NAND Targets connected to the CE\_n (Host Target).

4. If resetting each NAND Target sequentially, then:

a. Host issues Read Status (70 (FFh) of each NAND Target.

b. Host issues Reset (FFh). Th signal is high.

5. Host issues Read Status (70h) command and waits until SR[6] is set to one.

6. Host configures the NAND Target. Read Target.

7. Set Feature with a Feature Address of Volume Configuration is issued to appoint the Volume address for the NAND Target(s) whose ENi signal is high. The Volume address specified shall be unique amongst all NAND Targets. After the Set Features command completes, ENo is pulled high and the Volume is deselected until a Volume Select command is issued that selects the Volume. The host shall not issue another command to a NAND Target connected to the associated Host Target until after tFEAT time has elapsed.

8. For each NAND Target connected to the parallel initialization sequence.

9. When no further NAND Targets are four signal).

10. To complete the initialization process, a Volume Select command is issued following a CE\_n transition from high to low to select the next Volume that is going to execute a command.

Host issues Read Status (70h) command. Issuing Read Status (70h) prior to any other command indicates sequential Reset

Host issues Reset (FFh). This command only resets the NAND Target connected to the CE\_n (Host Target) whose ENi

6. Host configures the NAND Target. Read ID, Read Parameter Page, and other commands are issued as needed to configure the NAND

8. For each NAND Target connected to the Host Target, steps 4-7 are repeated for the sequential initialization sequence and steps 5-7 for

9. When no further NAND Targets are found connected to the Host Target, then repeat steps 2-8 for the next Host Target (i.e. host CE\_n

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 15

# 56

# **Config II: Discovery**

**Basic idea:**

- Go through and assign a different Volume Address (via Set Features) to each device on the same CE line

- Thereafter, each time you want to execute a given command (Read, Program, Erase, etc.) you need to pull **CE low and execute a Volume Select command first**

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 16

# **ONFI Cmd Se**

Read

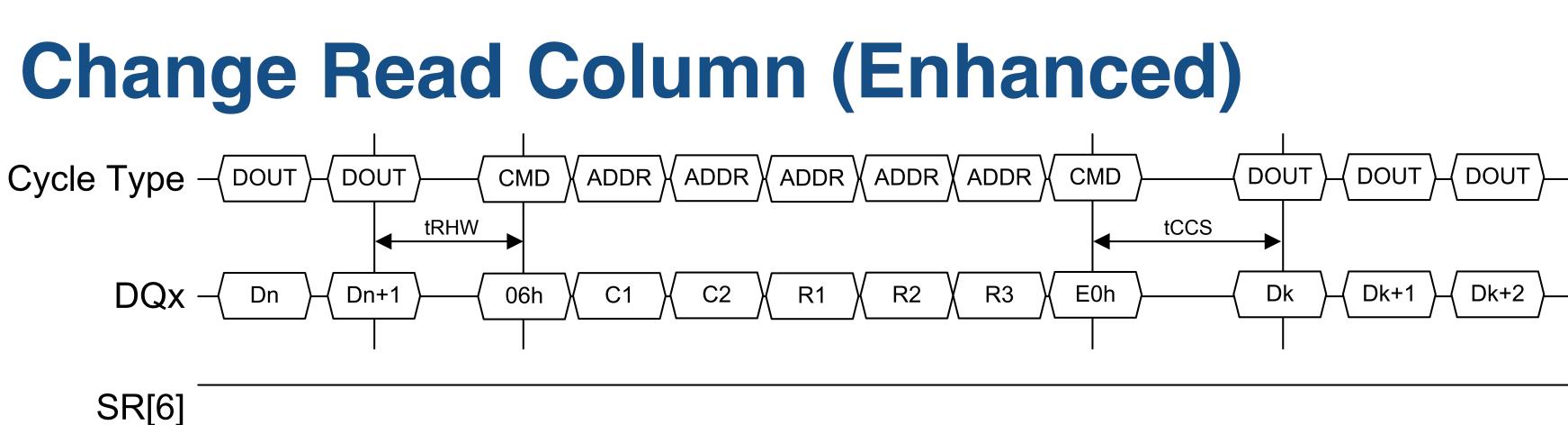

**Change Read Column Read Cache**

**Page Program** Page Cache Program

**Block Erase**

**Read Status Read ID Read Parameter Page**

| Э. |   |

|----|---|

|    | L |

|    |   |

| Command                       | O/M              | 1 <sup>st</sup> Cycle | 2 <sup>nd</sup><br>Cycle | Acceptable<br>while<br>Accessed<br>LUN is | Acceptable<br>while<br>Other<br>LUNs are | Target<br>level<br>command |

|-------------------------------|------------------|-----------------------|--------------------------|-------------------------------------------|------------------------------------------|----------------------------|

| Read                          | M                | 00h                   | 30h                      | Busy                                      | Busy                                     |                            |

| Multi-plane                   | 0                | 00h                   | 32h                      |                                           |                                          |                            |

| Copyback Read                 | 0                | 00h                   | 35h                      |                                           | Y                                        |                            |

| Change Read Colum             |                  | 05h                   | E0h                      |                                           | Y Y                                      |                            |

| Change Read Colum<br>Enhanced |                  | 06h                   | E0h                      |                                           | Y                                        |                            |

| Read Cache Randon             | n O              | 00h                   | 31h                      |                                           | Y                                        |                            |

| Read Cache<br>Sequential      | 0                | 31h                   |                          |                                           | Y                                        |                            |

| Read Cache End                | 0                | 3Fh                   |                          |                                           | Y                                        |                            |

| Block Erase                   | Μ                | 60h                   | D0h                      |                                           | Y                                        |                            |

| Multi-plane                   | 0                | 60h                   | D1h                      |                                           | Y                                        |                            |

| Read Status                   | Μ                | 70h                   |                          | Y                                         | Y                                        |                            |

| Read Status Enhanc            | ed O             | 78h                   |                          | Y                                         | Y                                        |                            |

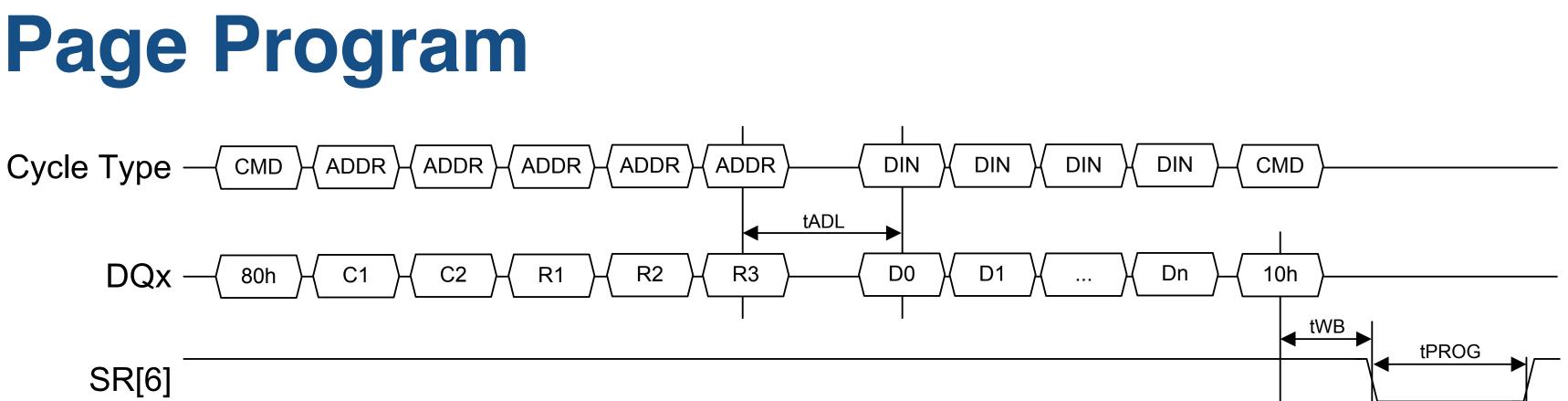

| Page Program                  | Μ                | 80h                   | 10h                      |                                           | Y                                        |                            |

| Multi-plane                   | 0                | 80h                   | 11h                      |                                           | Y                                        |                            |

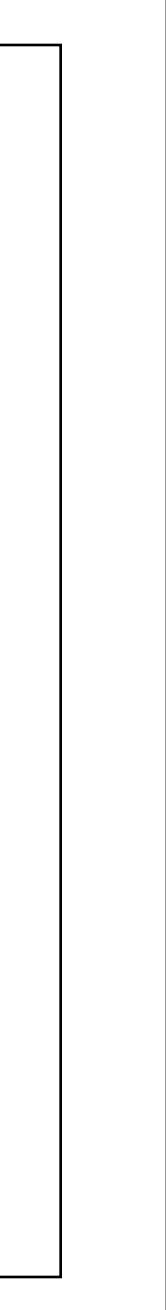

| Page Cache Progran            | n O              | 80h                   | 15h                      |                                           | Y                                        |                            |

| Copyback Program              | 0                | 85h                   | 10h                      |                                           | Y                                        |                            |

| Multi-plane                   | 0                | 85h                   | 11h                      |                                           | Y                                        |                            |

| Small Data Move <sup>2</sup>  | 0                | 85h                   | 11h                      |                                           | Y                                        |                            |

| Change Write Colum            | n <sup>1</sup> M | 85h                   |                          |                                           | Y                                        |                            |

| Change Row Addres             | $s^1 \mid O$     | 85h                   |                          |                                           | Y                                        |                            |

| Read ID                       | М                | 90h                   |                          |                                           |                                          | Y                          |

| Volume Select <sup>3</sup>    | 0                | E1h                   |                          | Y                                         | Y                                        |                            |

| ODT Configure <sup>3</sup>    | 0                | E2h                   |                          |                                           |                                          | Y                          |

| Read Parameter Pag            |                  | ECh                   |                          |                                           |                                          | Y                          |

| Read Unique ID                | 0                | EDh                   |                          |                                           |                                          | Y                          |

| Get Features                  | 0                | EEh                   |                          |                                           |                                          | Y                          |

| Set Features                  | 0                | EFh                   |                          |                                           |                                          | Y                          |

| LUN Get Features              | 0                | D4h                   |                          |                                           | Y                                        |                            |

| LUN Set Features              | 0                | D5h                   |                          |                                           | Y                                        |                            |

| Reset LUN                     | 0                | FAh                   | ļ                        | Y                                         | Y                                        |                            |

| Synchronous Reset             | 0                | FCh                   | ļ                        | Y                                         | Y Y                                      | Y                          |

| Reset                         | M                | FFh                   |                          | Y                                         | Y                                        | Y                          |

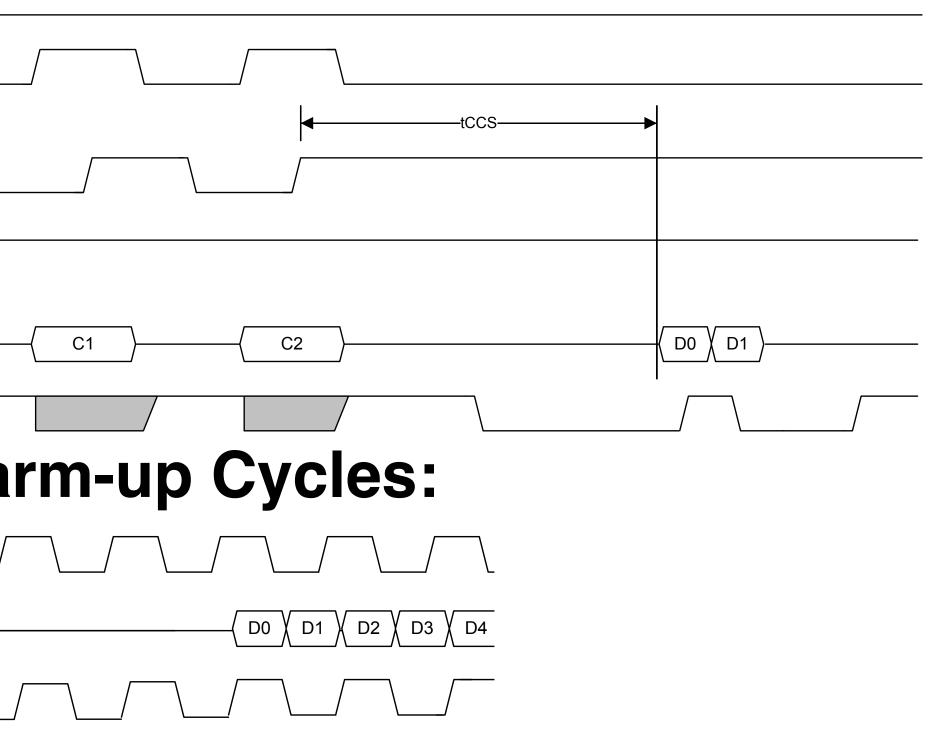

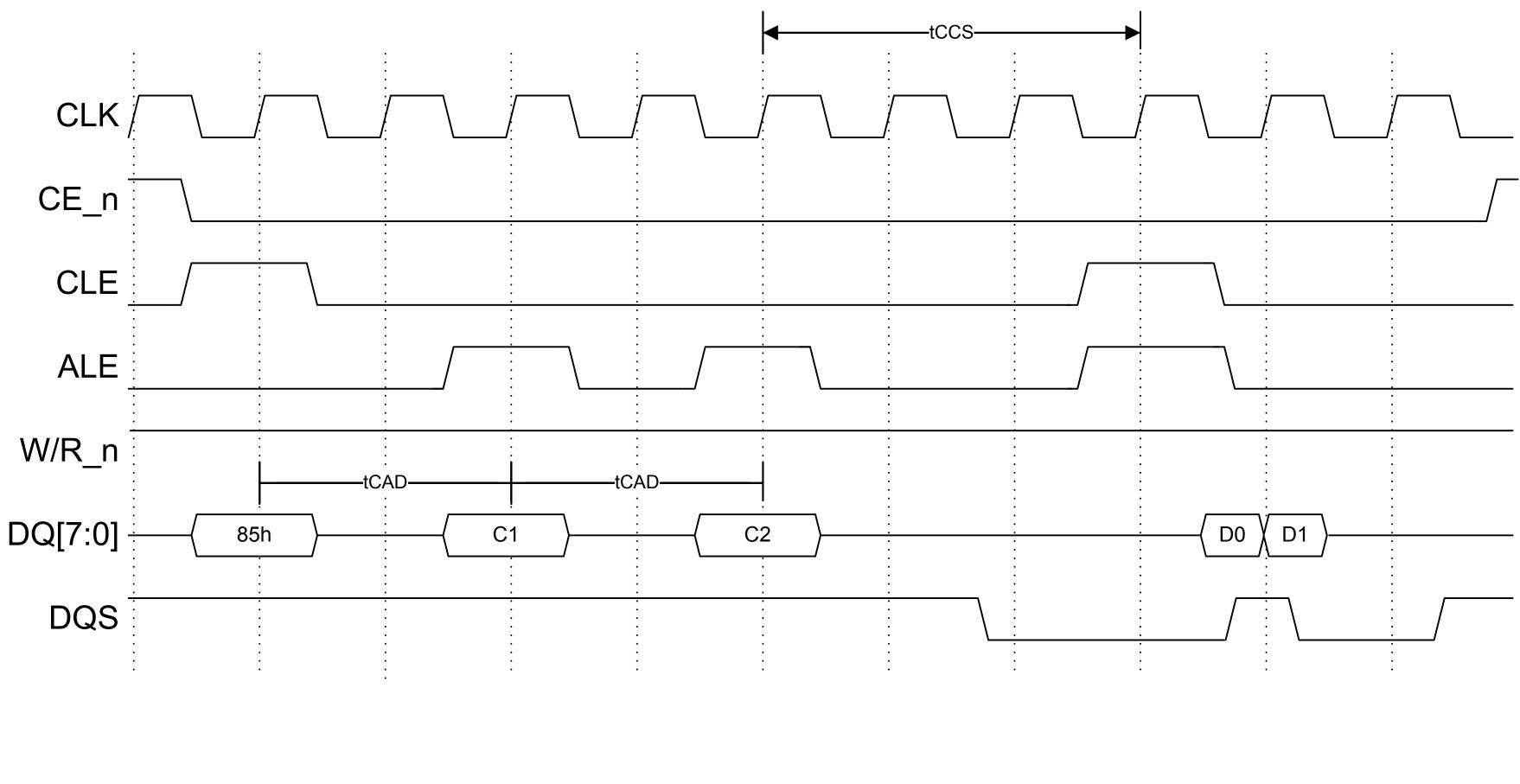

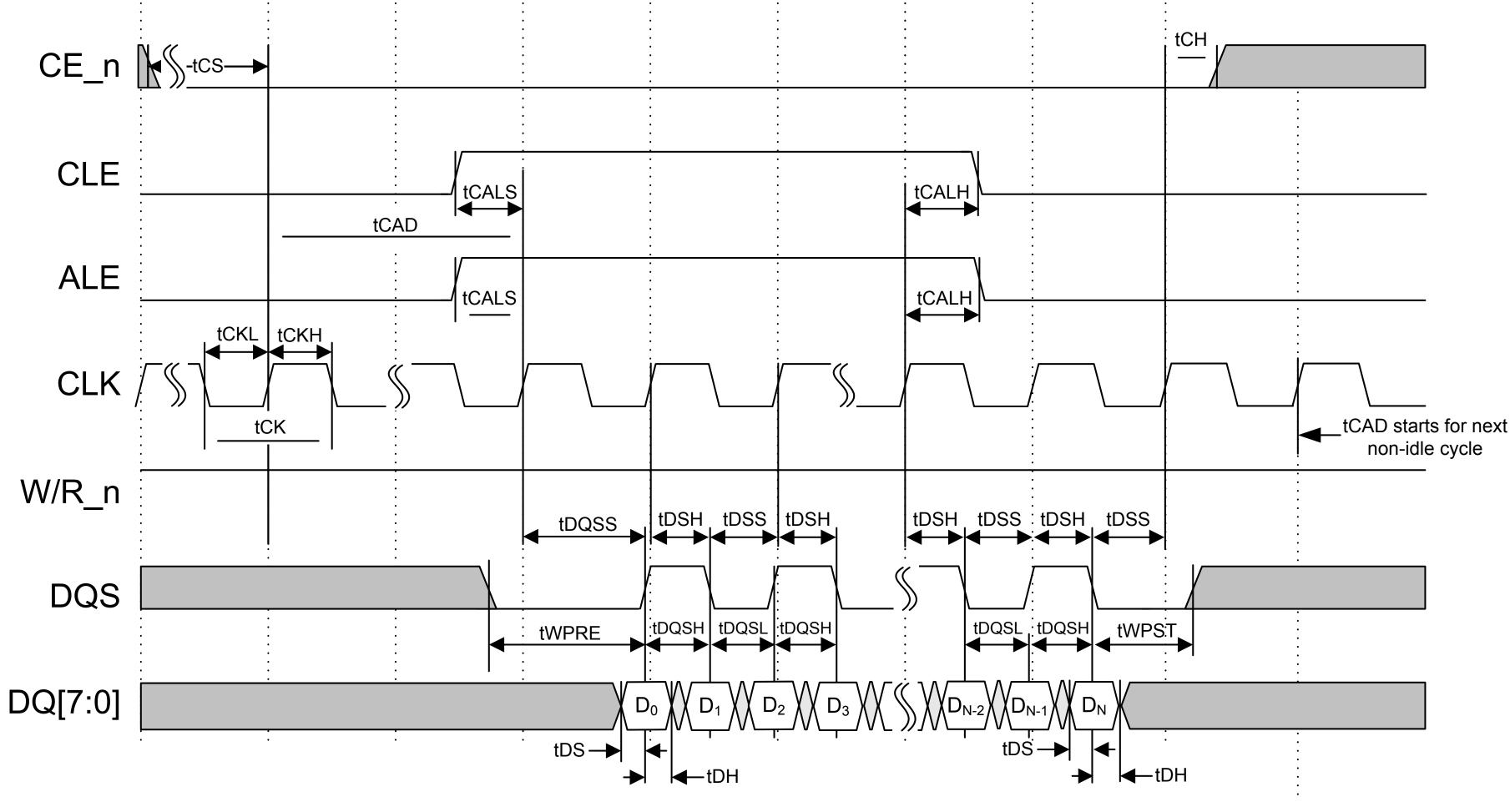

# Sending a Command (NV-DDR)

High-Speed Memory Systems

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 21

# **Read Parameter Page**

**Revision number, features supported** Manufacturer, product codes Data bytes per page, spare bytes per page Pages per block, blocks per LUN, number of LUNs Number of address cycles: row and column Number of bits per cell, number of planes Endurance info, bad block info, ECC info SDR, DDR, DDR2 timing mode support Electrical parameters, timing parameters, driver strength **CRC** bits at end ... plus, redundant copies of everything

Like Read ID, but returns 256-byte Parameter Page +more

University of Crete

SLIDE 22

Bruce Jacob

High-Speed

Spring 2014

Memory Systems

### CS-590.26 Lecture F

# **Read Status**

### Returns the status of the last command processed

| Value           | 7    | 6   | 5    | 4   | 3   | 2 | 1     | 0    |

|-----------------|------|-----|------|-----|-----|---|-------|------|

| Status Register | WP_n | RDY | ARDY | VSP | CSP | R | FAILC | FAIL |

FAIL FAILC R CSP VSP ARDY RDY WP n

reserved command-specific vendor-specific

- last command failed previous command failed

- Array Ready (if 1, no array operation in progress) if 1, LUN is ready for a command write-protect (active low)

### "Enhanced" version specifies row address

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 23

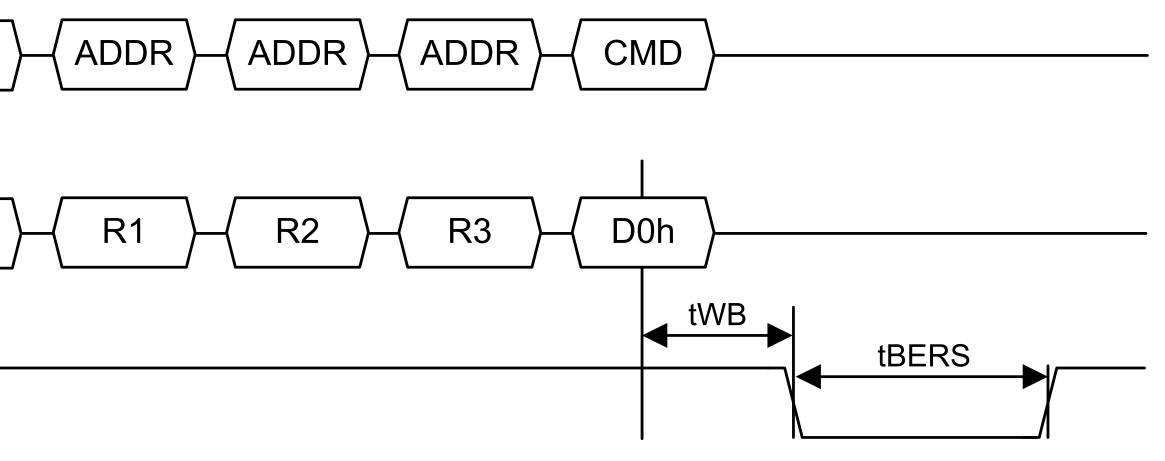

# **Block Erase**

### R1...R3 is row address (identifies device, block, page)

Cycle Type — CMD

DQ[7:0] — 60h

SR[6]

### Successful if SR[0] (FAIL) is zero afterward

Host may not attempt to erase a bad block (*i.e., it is the responsibility of the controller to know bad-block information & keep it up to date*)

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 24

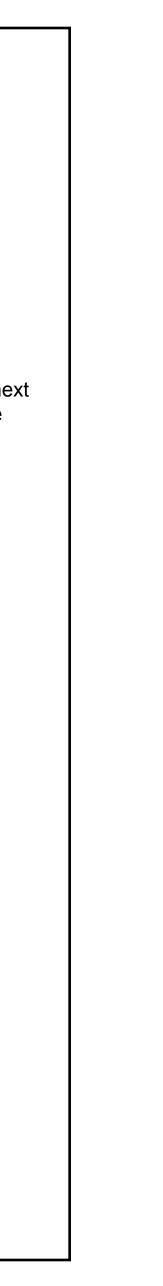

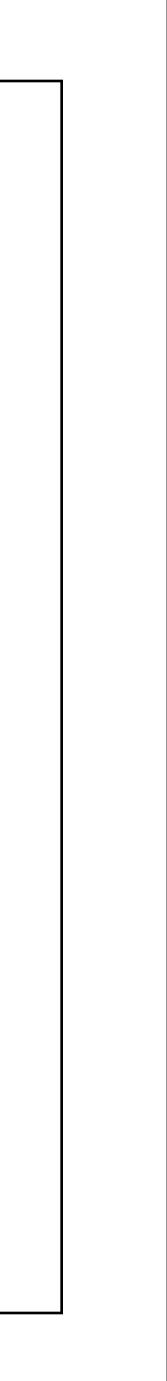

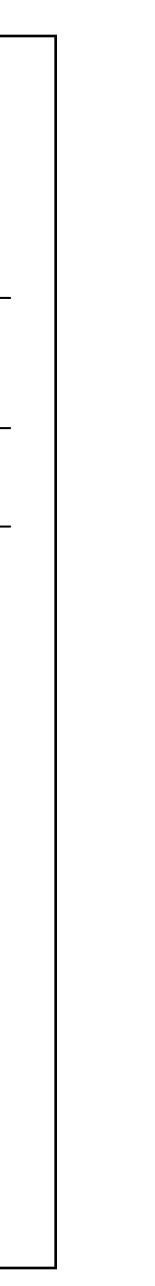

# **Read Page**

### C1...C3 is column address; R1...R3 is row address

# (via Read Status Enhanced)

- After tR (array-to-register), data is valid to be read out; controller should check the validity before bus transfer

- Second issuance of 00h starts data read-out on IO bus

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 25

**USE: Read Page** command issued to LUN 0 **Read Page** command issued to LUN 1

> **Read Status Enhanced** selects LUN 0 Change Read Column (Enhanced) issued to LUN 0 Data transferred from LUN 0

> Read Status Enhanced selects LUN 1 Change Read Column (Enhanced) issued to LUN 1 Data transferred from LUN 1

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 26

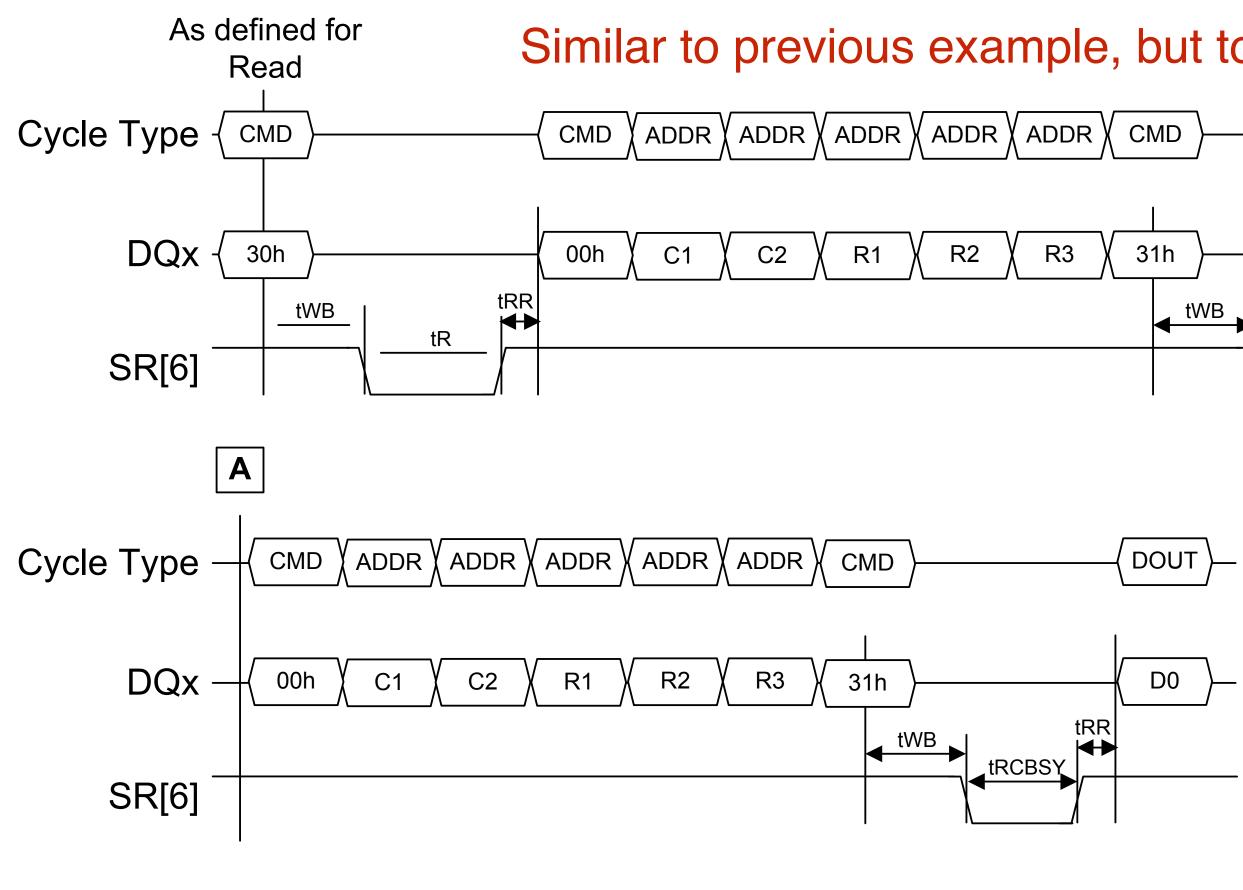

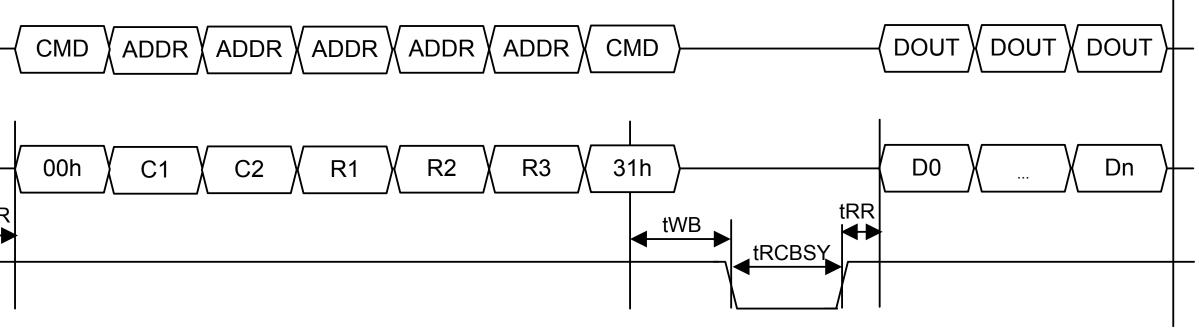

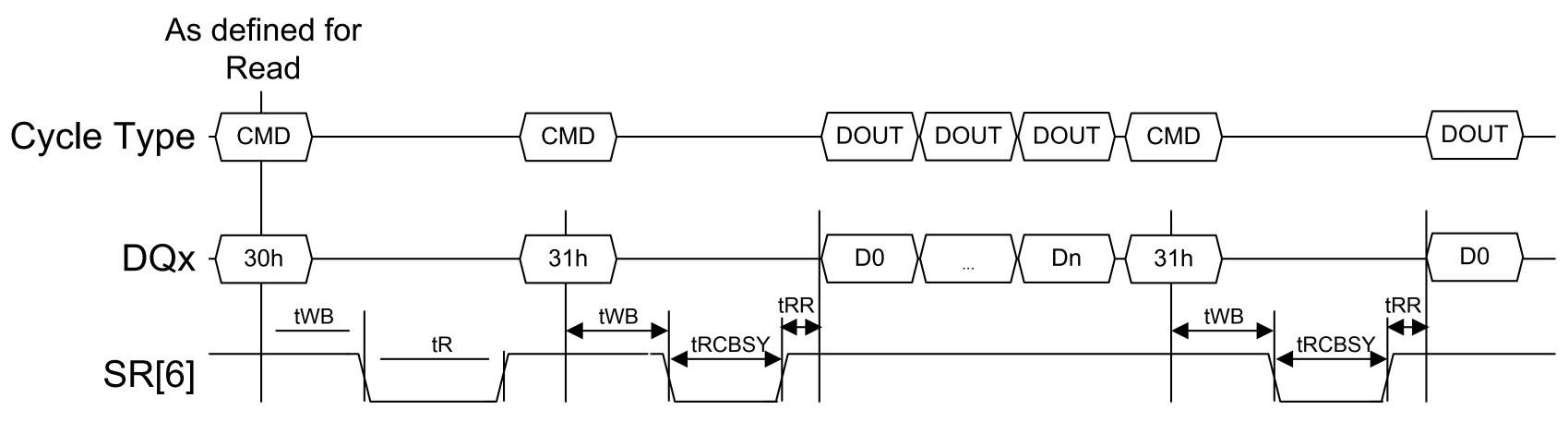

# **Read Cache (Random, Sequential, End) Read Cache Random (31h):**

Similar to previous example, but to the same LUN

Α

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 27

### **Read Cache Sequential (31h without address):**

### **Read Cache End (3Fh):**

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 28

### For operating one plane at a time

### For operating two or more planes ... (to overlap multiple program operations in time)

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 30

for example ...

# Other interesting commands

- **Copyback** (page copy within a single device)

- **Small Data Move (write less than a full page)**

- **Volume Select** (for addressing many devices on a CE)

- **Get/Set Features** (to read/change a device's parameters)

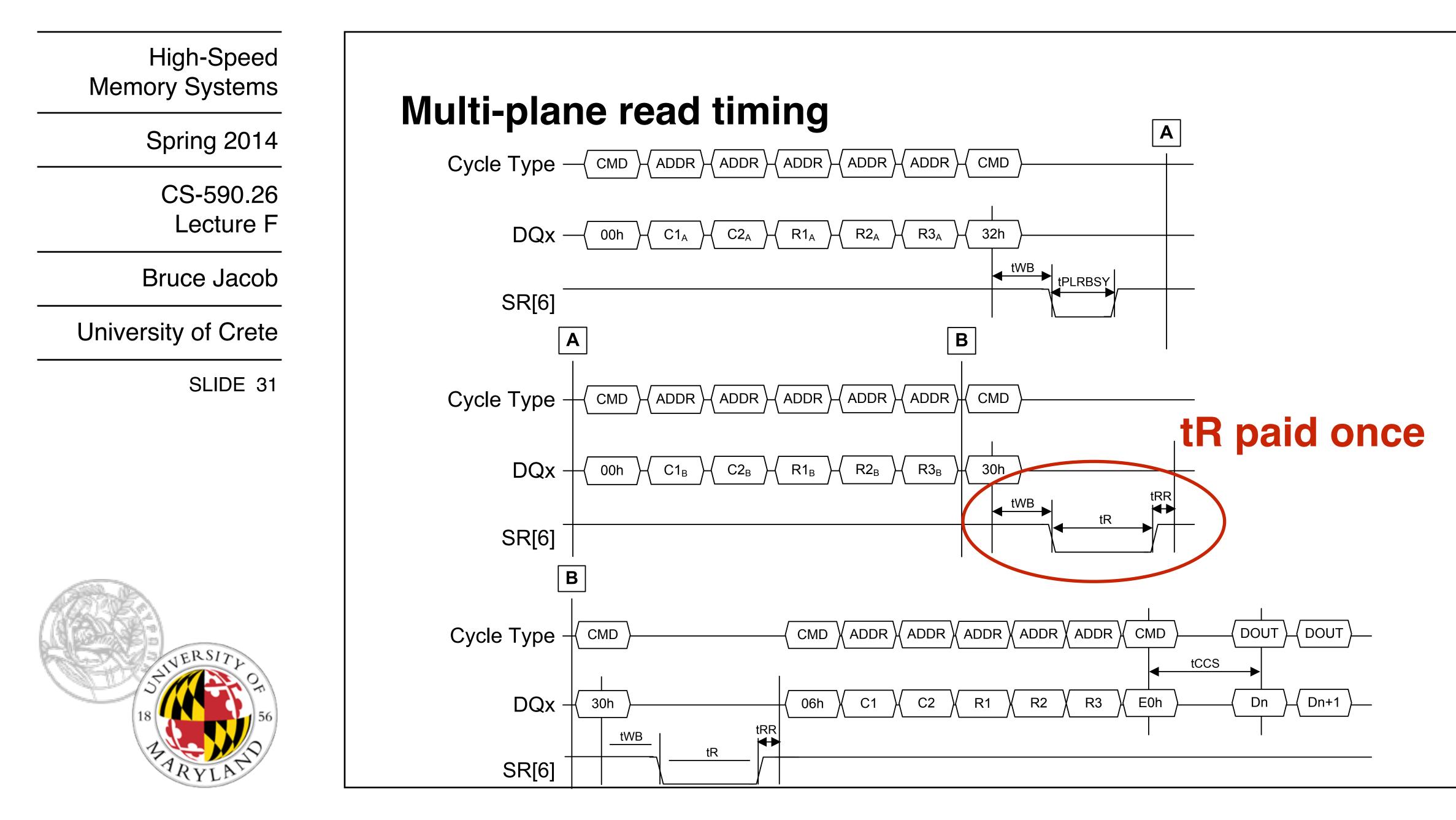

- Multi-plane Ops (Program, Copyback, Erase, Read) allows parallel or staggered commands to multiple planes

Spring 2014

CS-590.26 Lecture F

Bruce Jacob

University of Crete

SLIDE 32

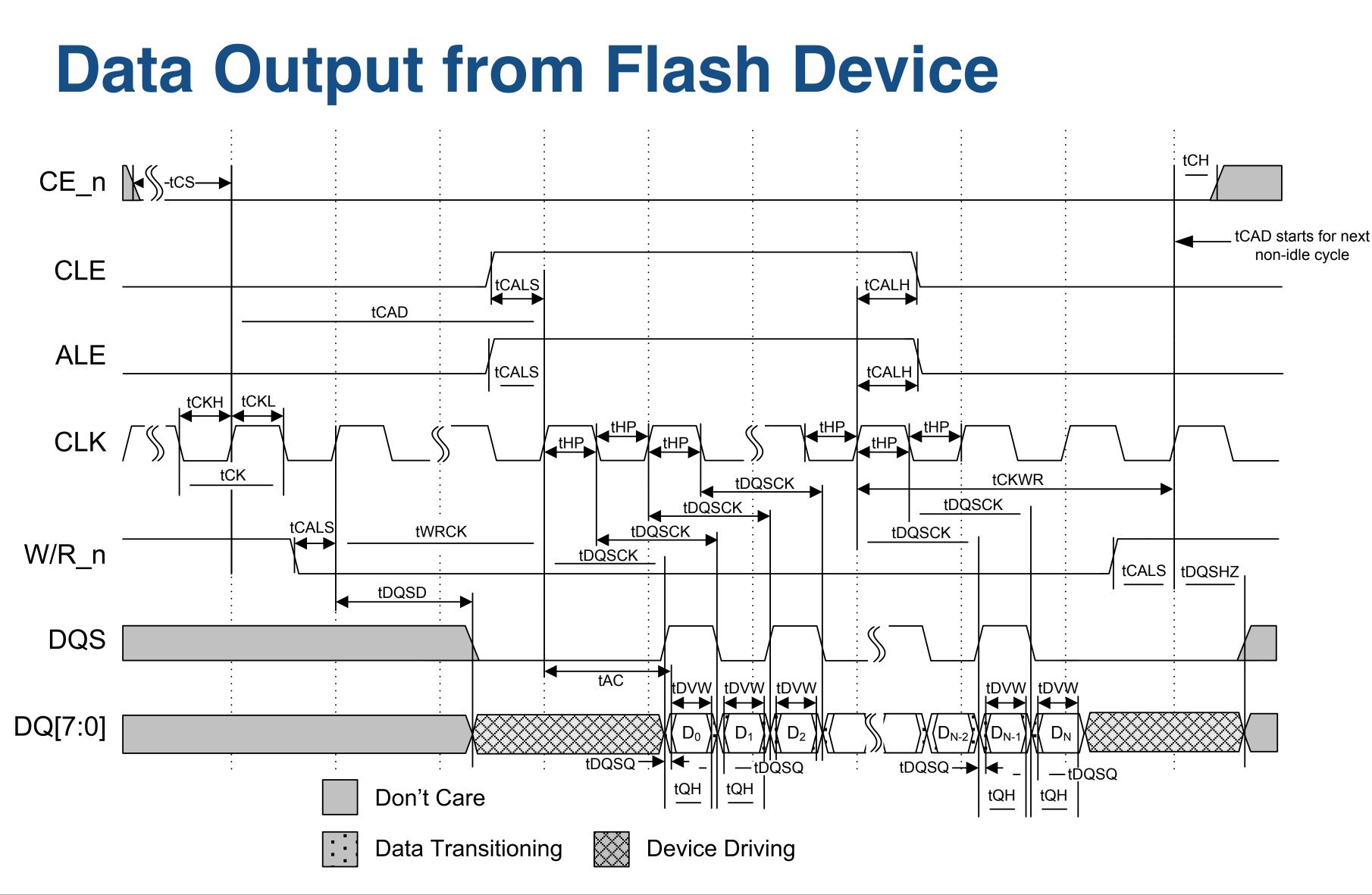

# **NV-DDR2 Differences**

# Differential signaling (e.g., DQS\_t and DQS\_c) & ODT CLK not used for command capture:

| CE_n \         |             |

|----------------|-------------|

|                | <pre></pre> |

| ALE            |             |

|                |             |

| WE_n \/        |             |

| RE_n           |             |

| DQ[7:0] — (85h |             |

| DQS            |             |

| ptional Data   | Wa          |

| RE_n           |             |

| DQ[7:0]        |             |

| DQS            | /           |

$\square$